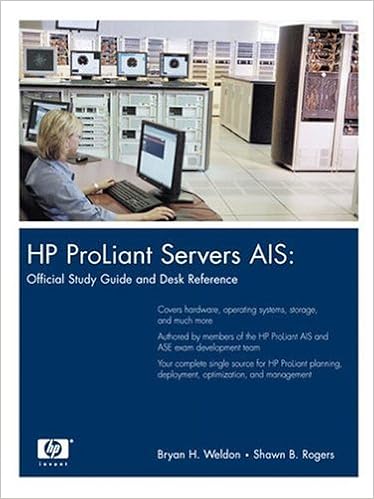

By Bryan H. Weldon, Shawn B. Rogers

ProLiant Servers AIS: reliable learn consultant and table ReferenceThe all-in-one HP ProLiant best-practice reference and HP qualified expert AIS prep guideHP ProLiant servers are the world's most generally deployed kinfolk of servers. HP's permitted Integration professional (AIS) or authorised platforms Engineer (ASE) certification demonstrates your services with those market-leading applied sciences - supplying you with a strong virtue in a hugely aggressive industry. Now, direct from HP, this is the respectable all-in-one research consultant for the AIS exam.Authored via contributors of HP's examination overview and approval staff, this booklet systematically stories each examination aim. It completely covers technology-related examination elements that aren't addressed in HP's 4-day AIS and 5-day ASE classes. whether you are not presently getting ready for certification, its systematic "best perform" insurance makes it an vital single-source reference for deploying, optimizing, and keeping HP ProLiant servers. insurance contains * Assessing company wishes and making plans for the implementation and progress of server-based IT infrastructure * figuring out the HP ProLiant product line and selecting the precise servers for any software * Reviewing key server subsystem applied sciences: procedure forums, processors, reminiscence, bus, chipsets, energy, racks, and extra * the easiest practices for deploying servers utilizing HP SmartStart and the fast Deployment Pack * coping with servers utilizing perception supervisor and distant perception Lights-Out version (RILOE) * making plans, identifying, deploying, and handling garage for ProLiant server environments * fitting andconfiguring home windows, Linux, and NetWare working platforms on ProLiant servers * Integrating, optimizing, functionality tuning, and troubleshooting ProLiant servers * Configuring, optimizing, and troubleshooting HP Array controllers and RAID subsystems"

Read or Download HP ProLiant Servers AIS: Official Study Guide and Desk Reference PDF

Best client-server systems books

Object-Oriented Project Management with UML

Just about all software program initiatives are dicy. The objective of each venture supervisor is to in some way take care of the fee and time table uncertainty whereas assembly your customer's wishes. In Object-Oriented venture administration with UML, Murray Cantor describes a sublime, UML-based method of handling object-oriented tasks sure to convey high quality software program on time and inside of funds.

Server+ is among the latest certifications from CompTIA, the sponsor of such vendor-neutral IT certifications as A+ and Network+. Server+ is located along community+ as a follow-up to A+ certification. The Server+ examination makes a speciality of community whereas the community+ examination makes a speciality of community software program.

Multi-Core Cache Hierarchies (Synthesis Lectures on Computer Architecture)

A key determinant of total method functionality and tool dissipation is the cache hierarchy in view that entry to off-chip reminiscence consumes many extra cycles and effort than on-chip accesses. moreover, multi-core processors are anticipated to put ever better bandwidth calls for at the reminiscence procedure. some of these concerns make it very important to prevent off-chip reminiscence entry through bettering the potency of the on-chip cache.

Over a hundred thirty complicated recipes to go looking, examine, installation, deal with, and display screen information successfully with ElasticSearch approximately This BookDeploy and deal with uncomplicated ElasticSearch nodes in addition to complicated cluster topologiesWrite local plugins to increase the functionalities of ElasticSearch to spice up your businessPacked with transparent, step by step recipes to stroll you thru the services of ElasticSearchWho This booklet Is ForIf you're a developer who implements ElasticSearch on your net functions and wish to sharpen your figuring out of the center parts and functions, this can be the ebook for you.

- Robohelp for the Web

- Sams Teach Yourself Sap R/3 in 10 Minutes

- Professional SQL Server 2005 XML

- Exchange 2000 Server Administration: A Beginner's Guide

- Ruling Distributed Dynamic Worlds

Additional resources for HP ProLiant Servers AIS: Official Study Guide and Desk Reference

Example text

Day Day Up > < Day Day Up > Summary This chapter explained the key concepts relating to processors and multiprocessing that you need to understand in order to properly recommend an HP ProLiant server solution. < Day Day Up > < Day Day Up > Learning Check 56 1: What is an instruction? 2: Match the processor component with its function. Prefetch unit A small, fast memory area that holds recently used instructions and data Decode unit A component that controls access to the address and data buses Execution unit A component that breaks an instruction into its constituent parts Control unit A small number of memory locations used by the control and execution units to store data temporarily Registers A register that stores recently taken branches to aid in branch prediction L1 cache A component that performs the actual data processing, such as adding and subtracting Branch target buffer A holding place for instructions and operands that a processor will need Bus interface unit A component that acts as a scheduler for the execution units Part ONE: Industry-Standard Server Technologies Part ONE: Industry-Standard Server Technologies 3: 57 Put the following steps in order to describe how a processor handles input: A.

If it is charged, the sense amp indicates a 1 on the Data Out pin. If it is not charged, the sense amp indicates a 0 on the Data Out pin. A memory cell can hold 1 bit of data, but a processor is designed to work with data in bytes. When the processor needs to store data in memory, it sends 8 bytes of data and an address through the system bus to the memory controller. The memory controller breaks each byte of data into 8 bits and uses the address that the processor sent to determine a row and column address.

During the recharge process, the memory chip cannot be used to send data to or receive data from the processor. The capacitors on a DRAM module are arranged in grids, sometimes called a memory matrix or a memory chip, as illustrated in Figure 4-3. The rows and columns of the grid are electrically conductive traces etched on the chip. The intersection of a row and column is called a cell. Each cell, which is identified by its row and column address, contains a transistor and a capacitor. Figure 4-3.